Choosing Number of Lanes -MIPI CSI

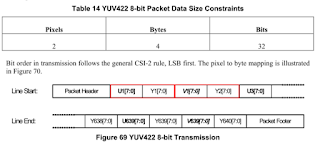

先說結論: Data Rate (bit/sec) = Sensor Resolution (pixel) * Packet Data Ratio (bit/pixel) * FPS (frame/s) * Overhead # of CSI Lane = Data Rate / Data BW per lane 其中Sensor Resolution以及FPS如同其名,不需要另外解釋;Overhead則是包括了Blanking data 的一個估計比例,通常為1.2~1.35。 但Packet Data Ratio就比較有趣,會隨各Camera module傳送給MIPI CSI Receiver的Data Format不一致,在MIPI CSI-2 ver.1.00中就定義了20種Sensor Data Format。其中7種明訂為“Primary Data Format”,規範CSI-2 Transmitter需要支援至少其中一種,而Receiver則是7種都要支援: 1. YUV422 8bit - 傳輸形式為U->Y->V->Y->…,對應的Packet Data Ratio = 32/2 = 16 (bit/pixel) 2. RGB888 - 傳輸形式為B->G->R->…,Packet Data Ratio = 24 (bit/pixel) 3. RGB565 - B[4:0]->G[5:0]->R[4:0]->…,16bit為一Packet,Packet Data Ratio = 16 (bit/pixel) 4. RAW8 - Packet Data Ratio = 8 (bit/pixel) 5. RAW10 - Packing 10-bit data into 8-bit data format,將每四組多出來的2 bits組合成另一個Byte,Packet Data Ratio = 40/4 = 10 (bit/pixel) 6. Generic 8-bit Long Packet Data 7. User Defined Byte-based Data - S...